Transistor–transistor logic (TTL) is a logic family built from bipolar junction transistors.

Its name signifies that transistors perform both the logic function

(the first "transistor") and the amplifying function (the second

"transistor"); it is the same naming convention used in resistor–transistor logic (RTL) and diode–transistor logic (DTL).

TTL integrated circuits (ICs) were widely used in applications such as computers, industrial controls, test equipment and instrumentation, consumer electronics, and synthesizers. Sometimes TTL-compatible logic levels are not associated directly with TTL integrated circuits, for example, they may be used at the inputs and outputs of electronic instruments.

After their introduction in integrated circuit form in 1963 by Sylvania, TTL integrated circuits were manufactured by several semiconductor companies. The 7400 series by Texas Instruments became particularly popular. TTL manufacturers offered a wide range of logic gates, flip-flops, counters, and other circuits. Variations of the original TTL circuit design offered higher speed or lower power dissipation to allow design optimization. TTL devices were originally made in ceramic and plastic dual-in-line (DIP) packages, and flat-pack form. TTL chips are now also made in surface-mount packages.

TTL became the foundation of computers and other digital electronics. Even after Very-large-scale integration integrated circuits made multiple-circuit-board processors obsolete, TTL devices still found extensive use as the glue logic interfacing between more densely integrated components.

TTL integrated circuits (ICs) were widely used in applications such as computers, industrial controls, test equipment and instrumentation, consumer electronics, and synthesizers. Sometimes TTL-compatible logic levels are not associated directly with TTL integrated circuits, for example, they may be used at the inputs and outputs of electronic instruments.

After their introduction in integrated circuit form in 1963 by Sylvania, TTL integrated circuits were manufactured by several semiconductor companies. The 7400 series by Texas Instruments became particularly popular. TTL manufacturers offered a wide range of logic gates, flip-flops, counters, and other circuits. Variations of the original TTL circuit design offered higher speed or lower power dissipation to allow design optimization. TTL devices were originally made in ceramic and plastic dual-in-line (DIP) packages, and flat-pack form. TTL chips are now also made in surface-mount packages.

TTL became the foundation of computers and other digital electronics. Even after Very-large-scale integration integrated circuits made multiple-circuit-board processors obsolete, TTL devices still found extensive use as the glue logic interfacing between more densely integrated components.

History

A real-time clock built of TTL chips around 1979.

TTL was invented in 1961 by James L. Buie of TRW,

which declared it, "particularly suited to the newly developing

integrated circuit design technology." The original name for TTL was transistor-coupled transistor logic (TCTL).

The first commercial integrated-circuit TTL devices were manufactured

by Sylvania in 1963, called the Sylvania Universal High-Level Logic

family (SUHL). The Sylvania parts were used in the controls of the Phoenix missile. TTL became popular with electronic systems designers after Texas Instruments introduced the 5400 series of ICs, with military temperature range, in 1964 and the later 7400 series, specified over a narrower range and with inexpensive plastic packages, in 1966.

The Texas Instruments 7400 family became an industry standard. Compatible parts were made by Motorola, AMD, Fairchild, Intel, Intersil, Signetics, Mullard, Siemens, SGS-Thomson, Rifa, National Semiconductor,

and many other companies, even in the Eastern Bloc (Soviet Union, GDR,

Poland, Czechoslovakia, Hungary, Romania - for details see 7400 series).

Not only did others make compatible TTL parts, but compatible parts

were made using many other circuit technologies as well. At least one

manufacturer, IBM, produced non-compatible TTL circuits for its own use; IBM used the technology in the IBM System/38, IBM 4300, and IBM 3081.

The term "TTL" is applied to many successive generations of bipolar

logic, with gradual improvements in speed and power consumption over

about two decades. The most recently introduced family 74Fxx is still

sold today (as of 2019), and was widely used into the late 90s. 74AS/ALS

Advanced Schottky was introduced in 1985.

As of 2008, Texas Instruments continues to supply the more

general-purpose chips in numerous obsolete technology families, albeit

at increased prices. Typically, TTL chips integrate no more than a few

hundred transistors each. Functions within a single package generally

range from a few logic gates to a microprocessor bit-slice.

TTL also became important because its low cost made digital techniques

economically practical for tasks previously done by analog methods.

The Kenbak-1, ancestor of the first personal computers, used TTL for its CPU instead of a microprocessor chip, which was not available in 1971. The Datapoint 2200 from 1970 used TTL components for its CPU and was the basis for the 8008 and later the x86 instruction set. The 1973 Xerox Alto and 1981 Star workstations, which introduced the graphical user interface, used TTL circuits integrated at the level of Arithmetic logic units (ALUs) and bitslices, respectively. Most computers used TTL-compatible "glue logic" between larger chips well into the 1990s. Until the advent of programmable logic, discrete bipolar logic was used to prototype and emulate microarchitectures under development.

Implementation

Fundamental TTL gate

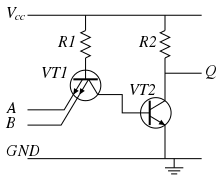

Two-input TTL NAND gate with a simple output stage (simplified).

TTL inputs are the emitters of bipolar transistors. In the case of NAND inputs, the inputs are the emitters of multiple-emitter transistors, functionally equivalent to multiple transistors where the bases and collectors are tied together. The output is buffered by a common emitter amplifier.

Inputs both logical ones. When all the inputs are held at

high voltage, the base–emitter junctions of the multiple-emitter

transistor are reverse-biased. Unlike DTL, a small “collector” current

(approximately 10µA) is drawn by each of the inputs. This is because the

transistor is in reverse-active mode.

An approximately constant current flows from the positive rail, through

the resistor and into the base of the multiple emitter transistor.

This current passes through the base–emitter junction of the output

transistor, allowing it to conduct and pulling the output voltage low

(logical zero).

An input logical zero. Note that the base–collector

junction of the multiple-emitter transistor and the base–emitter

junction of the output transistor are in series between the bottom of

the resistor and ground. If one input voltage becomes zero, the

corresponding base–emitter junction of the multiple-emitter transistor

is in parallel with these two junctions. A phenomenon called current

steering means that when two voltage-stable elements with different

threshold voltages are connected in parallel, the current flows through

the path with the smaller threshold voltage. That is, current flows out

of this input and into the zero (low) voltage source. As a result, no

current flows through the base of the output transistor, causing it to

stop conducting and the output voltage becomes high (logical one).

During the transition the input transistor is briefly in its active

region; so it draws a large current away from the base of the output

transistor and thus quickly discharges its base. This is a critical

advantage of TTL over DTL that speeds up the transition over a diode

input structure.

The main disadvantage of TTL with a simple output stage is the

relatively high output resistance at output logical "1" that is

completely determined by the output collector resistor. It limits the

number of inputs that can be connected (the fanout). Some advantage of the simple output stage is the high voltage level (up to VCC) of the output logical "1" when the output is not loaded.

A common variation omits the collector resistor of the output transistor, making an open-collector

output. This allows the designer to fabricate logic by connecting the

open-collector outputs of several logic gates together and providing a

single external pull-up resistor.

If any of the logic gates becomes logic low (transistor conducting),

the combined output will be low. Examples of this type of gate are the

7401 and 7403 series. Open-collector outputs of some gates have a higher maximum voltage, such as 15V for the 7426, useful when driving other than TTL loads.

TTL with a "totem-pole" output stage

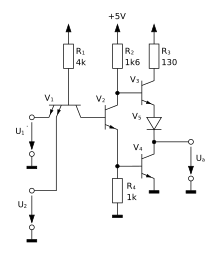

Standard TTL NAND with a "totem-pole" output stage, one of four in 7400

To solve the problem with the high output resistance of the simple

output stage the second schematic adds to this a "totem-pole" ("push–pull") output. It consists of the two n-p-n transistors V3 and V4, the "lifting" diode V5 and the current-limiting resistor R3 (see the figure on the right). It is driven by applying the same current steering idea as above.

When V2 is "off", V4 is "off" as well and V3 operates in active region as a voltage follower producing high output voltage (logical "1").

When V2 is "on", it activates V4, driving low voltage (logical "0") to the output. Again there is a current-steering effect: the series combination of V2's C-E junction and V4's B-E junction is in parallel with the series of V3 B-E, V5's anode-cathode junction, and V4 C-E. The second series combination has the higher threshold voltage, so no current flows through it, i.e. V3 base current is deprived. Transistor V3 turns "off" and it does not impact on the output.

In the middle of the transition, the resistor R3 limits the current flowing directly through the series connected transistor V3, diode V5 and transistor V4

that are all conducting. It also limits the output current in the case

of output logical "1" and short connection to the ground. The strength

of the gate may be increased without proportionally affecting the power

consumption by removing the pull-up and pull-down resistors from the

output stage.

The main advantage of TTL with a "totem-pole" output stage is the

low output resistance at output logical "1". It is determined by the

upper output transistor V3 operating in active region as an emitter follower. The resistor R3 does not increase the output resistance since it is connected in the V3

collector and its influence is compensated by the negative feedback. A

disadvantage of the "totem-pole" output stage is the decreased voltage

level (no more than 3.5 V) of the output logical "1" (even if the output

is unloaded). The reason of this reduction are the voltage drops across

the V3 base–emitter and V5 anode–cathode junctions.

Interfacing considerations

Like DTL, TTL is a current-sinking logic

since a current must be drawn from inputs to bring them to a logic 0

voltage level. The driving stage must absorb up to 1.6 mA from a

standard TTL input while not allowing the voltage to rise to more than

0.4 volts. The output stage of the most common TTL gates is specified to function

correctly when driving up to 10 standard input stages (a fanout of 10).

TTL inputs are sometimes simply left floating to provide a logical "1",

though this usage is not recommended.

Standard TTL circuits operate with a 5-volt

power supply. A TTL input signal is defined as "low" when between 0 V

and 0.8 V with respect to the ground terminal, and "high" when between

2 V and VCC (5 V),

and if a voltage signal ranging between 0.8 V and 2.0 V is sent into

the input of a TTL gate, there is no certain response from the gate and

therefore it is considered "uncertain" (precise logic levels vary

slightly between sub-types and by temperature). TTL outputs are

typically restricted to narrower limits of between 0.0 V and 0.4 V for a

"low" and between 2.4 V and VCC for a "high", providing at least 0.4 V of noise immunity.

Standardization of the TTL levels is so ubiquitous that complex

circuit boards often contain TTL chips made by many different

manufacturers selected for availability and cost, compatibility being

assured. Two circuit board units off the same assembly line on different

successive days or weeks might have a different mix of brands of chips

in the same positions on the board; repair is possible with chips

manufactured years later than original components. Within usefully

broad limits, logic gates can be treated as ideal Boolean devices

without concern for electrical limitations. The 0.4V noise margins are

adequate because of the low output impedance of the driver stage, that

is, a large amount of noise power superimposed on the output is needed

to drive an input into an undefined region.

In some cases (e.g., when the output of a TTL logic gate needs to

be used for driving the input of a CMOS gate), the voltage level of the

"totem-pole" output stage at output logical "1" can be increased closer

to VCC by connecting an external resistor between the V3 collector and the positive rail. It pulls up the V5 cathode and cuts-off the diode.

However, this technique actually converts the sophisticated

"totem-pole" output into a simple output stage having significant output

resistance when driving a high level (determined by the external

resistor).

Packaging

Like most integrated circuits of the period 1963–1990, commercial TTL devices are usually packaged in dual in-line packages (DIPs), usually with 14 to 24 pins, for through-hole

or socket mounting. Epoxy plastic (PDIP) packages were often used for

commercial temperature range components, while ceramic packages (CDIP)

were used for military temperature range parts.

Beam-lead

chip dies without packages were made for assembly into larger arrays as

hybrid integrated circuits. Parts for military and aerospace

applications were packaged in flatpacks, a form of surface-mount package, with leads suitable for welding or soldering to printed circuit boards. Today,

many TTL-compatible devices are available in surface-mount packages,

which are available in a wider array of types than through-hole

packages.

TTL is particularly well suited to bipolar integrated circuits

because additional inputs to a gate merely required additional emitters

on a shared base region of the input transistor. If individually

packaged transistors were used, the cost of all the transistors would

discourage one from using such an input structure. But in an integrated

circuit, the additional emitters for extra gate inputs add only a small

area.

At least one computer manufacturer, IBM, built its own flip chip integrated circuits with TTL; these chips were mounted on ceramic multi-chip modules.

Comparison with other logic families

TTL devices consume substantially more power than equivalent CMOS devices at rest, but power consumption does not increase with clock speed as rapidly as for CMOS devices. Compared to contemporary ECL

circuits, TTL uses less power and has easier design rules but is

substantially slower. Designers can combine ECL and TTL devices in the

same system to achieve best overall performance and economy, but

level-shifting devices are required between the two logic families. TTL

is less sensitive to damage from electrostatic discharge than early CMOS devices.

Due to the output structure of TTL devices, the output impedance

is asymmetrical between the high and low state, making them unsuitable

for driving transmission lines. This drawback is usually overcome by

buffering the outputs with special line-driver devices where signals

need to be sent through cables. ECL, by virtue of its symmetric

low-impedance output structure, does not have this drawback.

The TTL "totem-pole" output structure often has a momentary

overlap when both the upper and lower transistors are conducting,

resulting in a substantial pulse of current drawn from the power supply.

These pulses can couple in unexpected ways between multiple integrated

circuit packages, resulting in reduced noise margin and lower

performance. TTL systems usually have a decoupling capacitor

for every one or two IC packages, so that a current pulse from one TTL

chip does not momentarily reduce the supply voltage to another.

Several manufacturers now supply CMOS logic equivalents with

TTL-compatible input and output levels, usually bearing part numbers

similar to the equivalent TTL component and with the same pinouts. For example, the 74HCT00 series provides many drop-in replacements for bipolar 7400 series parts, but uses CMOS technology.

Sub-types

Successive

generations of technology produced compatible parts with improved power

consumption or switching speed, or both. Although vendors uniformly

marketed these various product lines as TTL with Schottky diodes, some of the underlying circuits, such as used in the LS family, could rather be considered DTL.

Variations of and successors to the basic TTL family, which has a

typical gate propagation delay of 10ns and a power dissipation of 10 mW

per gate, for a power–delay product (PDP) or switching energy of about 100 pJ, include:

- Low-power TTL (L), which traded switching speed (33ns) for a reduction in power consumption (1 mW) (now essentially replaced by CMOS logic)

- High-speed TTL (H), with faster switching than standard TTL (6ns) but significantly higher power dissipation (22 mW)

- Schottky TTL (S), introduced in 1969, which used Schottky diode clamps at gate inputs to prevent charge storage and improve switching time. These gates operated more quickly (3ns) but had higher power dissipation (19 mW)

- Low-power Schottky TTL (LS) – used the higher resistance values of low-power TTL and the Schottky diodes to provide a good combination of speed (9.5ns) and reduced power consumption (2 mW), and PDP of about 20 pJ. Probably the most common type of TTL, these were used as glue logic in microcomputers, essentially replacing the former H, L, and S sub-families.

- Fast (F) and Advanced-Schottky (AS) variants of LS from Fairchild and TI, respectively, circa 1985, with "Miller-killer" circuits to speed up the low-to-high transition. These families achieved PDPs of 10 pJ and 4 pJ, respectively, the lowest of all the TTL families.

- Low-voltage TTL (LVTTL) for 3.3-volt power supplies and memory interfacing.

Most manufacturers offer commercial and extended temperature ranges: for example Texas Instruments 7400 series parts are rated from 0 to 70 °C, and 5400 series devices over the military-specification temperature range of −55 to +125 °C.

Special quality levels and high-reliability parts are available for military and aerospace applications.

Radiation-hardened devices (for example from the SNJ54 series) are offered for space applications.

Applications

Before the advent of VLSI

devices, TTL integrated circuits were a standard method of construction

for the processors of mini-computer and mainframe processors; such as

the DEC VAX and Data General Eclipse, and for equipment such as machine tool numerical controls, printers and video display terminals. As microprocessors

became more functional, TTL devices became important for "glue logic"

applications, such as fast bus drivers on a motherboard, which tie

together the function blocks realized in VLSI elements.

Analog applications

While

originally designed to handle logic-level digital signals, a TTL

inverter can be biased as an analog amplifier. Connecting a resistor

between the output and the input biases the TTL element as a negative feedback amplifier.

Such amplifiers may be useful to convert analog signals to the digital

domain but would not ordinarily be used where analog amplification is

the primary purpose. TTL inverters can also be used in crystal oscillators where their analog amplification ability is significant.

A TTL gate may operate inadvertently as an analog amplifier if

the input is connected to a slowly changing input signal that traverses

the unspecified region from 0.8 V to 2 V. The output can be erratic when

the input is in this range. A slowly changing input like this can also

cause excess power dissipation in the output circuit. If such an analog

input must be used, there are specialized TTL parts with Schmitt trigger

inputs available that will reliably convert the analog input to a

digital value, effectively operating as a one bit A to D converter.

![{\displaystyle -{\frac {\mathrm {d} ^{2}V}{\mathrm {d} x^{2}}}={\frac {\rho }{\varepsilon }}={\frac {q}{\varepsilon }}\left[(P_{0}-N_{0})+(C_{D}-C_{A})\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e906c406ff6246e9e44eb60f9848f08e369e0b3a)

![{\displaystyle \Delta V=\int _{D}\int {\frac {q}{\varepsilon }}\left[(P_{0}-N_{0})+(C_{D}-C_{A})\right]\,\mathrm {d} x\,\mathrm {d} x}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e0a9e5aec3cf283bc949fc8849155b5d6eadf478)